# 九州大学学術情報リポジトリ Kyushu University Institutional Repository

# タイミングエラーの予報を目的とするカナリアFFの 挿入位置限定

國武, 勇次 九州大学大学院システム情報科学府

佐藤, 寿倫 福岡大学工学部電子情報工学科 | 九州大学大学院システムLSI 研究センター

山口, 誠一朗 九州大学大学院システム情報科学府

安浦, 寬人 独立行政法人科学技術振興機構, CREST

https://hdl.handle.net/2324/12560

出版情報:電子情報通信学会技術研究報告 VLD2008-74, DC2008-42, pp.85-89, 2008-11. 電子情報通信

. バージョン: 権利関係:

# タイミングエラーの予報を目的とするカナリアFFの挿入位置限定

† 九州大学大学院システム情報科学府 †† 福岡大学工学部電子情報工学科 ††† 九州大学大学院システム LSI 研究センター †††† 九州大学大学院システム情報科学研究院 \* 独立行政法人科学技術振興機, CREST

あらまし 半導体製造技術の進展に伴い、プロセスばらつき、電源電圧のゆらぎや温度変化などが回路遅延に与える影響が増加している。我々はこれらの回路遅延の変化により発生するタイミングエラーを予報する機構としてカナリア FF を提案している。カナリア FF は通常の FF を二重化する構造をもつため、適用するにあたって面積の増加が問題となる。本論文では、面積増加を抑制するためにカナリア FF の挿入位置の限定方法を提案しその評価を行う。キーワード ばらつき、動的電圧制御、信頼性、クリティカルパス、最悪ケース指向設計

# Insertion-Point Selection of Canary FF for Timing Error Prediction

Kunitake YUJI<sup>†</sup>, Sato TOSHINORI<sup>††,†††\*</sup>, Seiichiro YAMAGUCHI<sup>†</sup>, and Yasuura HIROTO<sup>††††\*</sup>

† Graduate School of Information Science and Electrical Engineering, Kyushu University

†† Department of Electronics Engineering and Computer Science, Fukuoka University

††† System LSI Research Center, Kyushu University

†††† Faculty of Information Science and Electrical Engineering, Kyushu University

\* Japan Science and Technology Agency, CREST

Abstract The deep submicron semiconductor technologies increase parameter variations. The increase in parameter variations requires excessive design margin that has serious impact on performance and power consumption. In order to eliminate the excessive design margin, we are investigating canary logic. The canary logic requires additional circuits consisting of a Flip-Flop (FF) and a comparator. Thus, the canary logic suffers large area overhead. In order to reduce the area overhead, this paper proposes an insertion point selection strategy of canary FF and evaluates it.

Key words variation, Dynamic Voltage Scaling, reliability, critical path, worst-case design

### 1. まえがき

半導体微細化技術の進展に伴って素子特性のばらつきが増加している [2], [6] . 製造時に生じるプロセスばらつき, IR ドロップやグラウンドバウンスによって引き起こされる電源電圧のゆらぎ,そしてチップ内の局所的な温度変化によって,素子特性にばらつきが生じる.これにより同じプロセスで製造した個々のチップに性能差が生じ,タイミング歩留まりの低下を引き起こす.従来の設計では,タイミング歩留まりの低下を抑制するために,素子特性のばらつきの最悪ケースを考慮してタイミングマージンが取られてきた.しかしこれらのばらつきが増加すると,一定のタイミング歩留まりを達成するために必要なタイミングマージンが増大してしまう.タイミングマージンの増大は性能および消費電力に大きな影響を与えるため,最悪ケース

を考慮した設計では目標仕様を満たすことが非常に困難となる.

この問題に対処するために,近年タイミングエラー検出フリップフロップ (FF) を備える DVS システムにより過剰なタイミングマージンを削減する手法の研究が盛んに行われている [1], [3], [4], [7]. マイクロプロセッサの動作時にタイミングエラーを検出し,DVS により正常動作に必要な電圧を供給する.これにより過剰に見積もられたタイミングマージンを取り除くことを試みている.我々もこれらの手法と同様に,タイミングエラー検出 FF としてカナリア FF を利用する DVS システムを検討している [5].

これらの,タイミングエラー検出 FF を備えた DVS システムには共通する問題が存在する.タイミングエラー検出 FF は通常の FF と比べて面積が大きいため,マイクロプロセッサの面積増加を引き起こす.さらに,エラーを収集するための回路

や DVS を行うための付加回路によっても面積が増加する.面積の増加はそれによる消費エネルギーとチップの製造コストを増加させる.本稿ではこの面積増加の問題について考察し,問題解決策の検討と評価を行う.

以下に本稿の構成について説明する.2 節でタイミングエラー検出 FF について関連研究を紹介し,特にカナリア FF について詳しく説明する.3 節でタイミングエラー検出 FF の面積増加の問題を考察する.4 節で面積のオーバーヘッドの抑制手法を提案し,5 節で提案手法の評価結果を示す.6 節で今後の課題を示し,7 節で本論文をまとめる.

### 2. タイミングエラー検出 FF

#### 2.1 関連研究

近年,タイミングエラー検出 FF を利用することで DVS を行う研究が盛んに行われている.このようなタイミングエラーを検出する FF として,Razor Flip-Flops (RazorFF) [3],RazorII [1],Phase-adjustable Error Detection Flip-Flop (PEDFF) [7],Delay-Compensation Flip-Flops (DCFF) [4] など多数の FF が提案されている.

RazorFF は、通常の FF(メイン FF) に加えシャドウ FF と呼ばれる FF を持つ・シャドウ FF には遅延クロックが供給されるため、前段からの信号をラッチするタイミングがメイン FF に比べて遅い・言い替えるとシャドウ FF はメイン FF に比べタイミング制約が緩和されている・したがって、メイン FF でタイミングエラーが発生してもシャドウ FF には正しい値が保持されていることが期待できる・この 2 つの FF の値を比較することでタイミングエラーを検出する・タイミングエラーにより発生した故障状態は備えられている故障回復機構により正しい状態へ回復される・

RazorII は RazorFF のタイミング制約の緩和と面積を削減する目的で提案されている.RazorII では FF を 2 重化する変わりに,Detection Clock Generator (DCG) と Transition Detector (TD) が用いられる.DCG によりクロック信号の立上りとデータ信号の立上りのタイミングを検出し TD で比較することによってタイミングエラーを検出する.設計事例によると RazorFF はトランジスタ数 76 個で設計可能であるのに対して RazorII はトランジスタ数 47 個で設計可能であり,約 3 分の 2 まで面積の削減に成功している.

PEDFF の基本構造は RazorFF と同じように遅延クロックを利用することでタイミングエラーを検出する. さらに PEDFFでは,クロックゲーティングデザインに対応する方法が提案されている.クロックゲーティングされた FF はディスエーブル期間中のデータ信号に対するエラー検出モニターが必要となる. しかし,これは毎サイクルデータとイネーブル信号のセットアップ違反をチェックする必要があるため,クロックゲーティングの効果が失われてしまう. そこで,PEDFF ではイネーブル信号を切り離して合計四つの FF でデータとイネーブル信号のエラーを検出する.

DCFF は, FF のマスター側のラッチにクロック信号の変わりに Gate と呼ばれる信号を供給する. FF へのデータ信号が

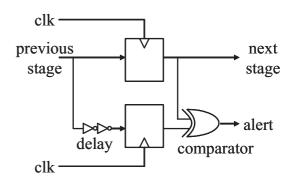

図 1 カナリア FF

不安定なときにクロック信号が立ち上がるとタイミングエラーを検出し、FF へのデータ信号が安定した後で Gate 信号を立ち上げる.この Gate 信号に動機してマスター側のラッチが動作することで、タイミングエラーを回避することができる.

### 2.2 カナリア FF

図 1 に我々の提案しているカナリア FF の回路を示す.カナリア FF は,通常の FF(メイン FF) に対して,RazorFF 同様にシャドウ FF を用意する.ただし,カナリア FF ではメイン FF で発生するタイミングエラーを検出する目的ではなく,メイン FF で発生しようとするタイミングエラーを予報する目的で利用される.カナリア FF ではシャドウ FF の直前に遅延素子が挿入されるため,シャドウ FF の方がメイン FF よりもタイミング制約が厳しくなる.従って,シャドウ FF の方がメイン FF よりもタイミングエラーに遭遇しやすい.メイン FF とシャドウ FF に取り込まれた値を比較し,一致しなかった場合にメイン FF で発生しようとしているタイミングエラーが予報される.

カナリアFFを含め、タイミングエラー検出FFは通常のFFに加えタイミングエラーを検出するための回路が付加される.このため通常のFFをタイミングエラー検出FFに置き換えると回路全体の面積に大きな影響を与える.以降の節では,この面積のオーバーヘッドの問題について言及する.

# 3. 面積のオーバーヘッドの問題

カナリア FF を利用する DVS システムでは,通常の FF をカナリア FF に置き換えるため,それによる面積の増加が問題となる.図 1 に示すようにカナリア FF はメイン FF に加え,シャドウ FF,遅延素子そしてエラー予報検出のための XORゲートが追加される.VDEC より提供されている 65nm スタンダードセルライブラリを参考にしてカナリア FF のレイアウト設計を実施した.その結果,通常の FF と比べて面積はおよそ 2.65 倍となった.このとき選択した遅延素子と XOR ゲートはライブラリ中の面積最小のものを選択している.遅延素子の遅延量や XOR の駆動力を考慮すると面積はさらに増加する.この面積のオーバーヘッドの問題はカナリア FF に限らず,他のタイミングエラー検出 FF でも問題となる.PEDFF [7] の場合は,通常の FF の面積の 3.1 倍となることが報告されている.

さらに , カナリア FF を利用する DVS システムではチップ

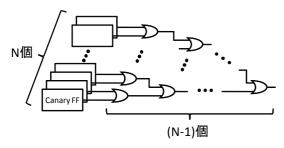

図 2 エラー予報収集回路

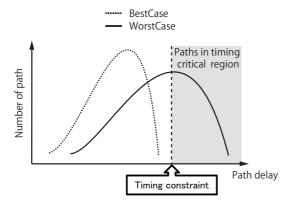

図3 電源電圧の上限と下限のパス遅延分布

内の全てのカナリア FF のうち一つでもタイミングエラーが予報されると電源電圧を降圧する必要がある.このためチップ内の全てのカナリア FF のタイミングエラー予報信号を収集する必要がある.例えば,図 2 に示すように全てのカナリア FF のエラー予報収集回路を OR ゲートで構成すると,N 個のカナリア FF に対して N-1 個の OR ゲートが必要となる.カナリア FF はチップ全体に点在すると考えられるため,エラー予報収集回路の配線長は長くなり面積に与える影響はさらに大きくなると考えられる.

さらに, DVS を行う制御回路による面積への影響もある.

# 4. 面積のオーバーヘッド抑制手法

前節で述べたように , カナリア FF を利用する DVS システムは通常の FF をカナリア FF への置換することで面積が増加する . そこで , 面積の増加を抑制するために回路のパスの遅延分布を利用してカナリア FF の挿入位置の限定を行う .

論理段数や配線長によって個々の回路パスの遅延時間は異なる.したがって,遅延時間が短い回路パスは DVS により下限電圧が選択されてもタイミングエラーを起こさないものが存在する.つまり,これらのパスの出力側に接続される FF をカナリア FF に置き換えてもエラーは予報されない.そこで,タイミングエラーを起こす可能性のあるパスを特定し,その出力側に接続される FF のみをカナリア FF と置換することでカナリア FF とそのタイミングエラー予報収集のための回路の面積を抑制することができる.以降,本論文ではタイミングエラーを発生するパスの出力側に接続される FF をタイミング違反 FF と記す.

図3にタイミングエラーを起こす可能性を持つパスの限定方

表 1 65nm スタンダードセルライブラリ

| Vdd   | Temperature | Process | -         |

|-------|-------------|---------|-----------|

| 1.3V  | 125 °C      | Fast    | Synthesis |

| 1.2V  | 25 °C       | Typical |           |

| 1.1V  | 125 °C      | Slow    |           |

| 1.05V | 125 °C      | Slow    |           |

表 2 評価対象回路の諸元

|                     | MeP              | M32R              |

|---------------------|------------------|-------------------|

| clock cycle time    | 2.5ns            | 5.5 ns            |

| Number of FFs       | 3721             | 10585             |

| Area of normal chip | $260489 \mu m^2$ | $8028585 \mu m^2$ |

| Pipline             | 5stage           | 5stage            |

法を示す.まず,DVS で選択可能な電源電圧の上限電圧 (Best-Case) で論理合成を行いタイミングレポートを基に目標性能を決定する. $^{(3\pm 1)}$ 次に下限電圧 (WorstCase) のコーナー条件を用いて STA を行い,全てのタイミングエラー違反 FF をカナリア FF に置き換える.このときタイミング制約を満たす FF は下限電圧のコーナー条件時の遅延を越えることはないため動作は保証される.論文 [7] では下限電圧を決定するために,我々と同様の方法でタイミング違反 FF を特定し,それらを PEDFFに置換している.そのときの消費エネルギーの見積りから最もエネルギー利用効率のよい場合の電源電圧を下限電圧として決定している.1.0V-0.65V の範囲で評価した結果,最適な電源電圧は 0.7V であり,このときの置換される FF の割合はチップ内の FF の総数の約 10%程度であることが報告されている.

# 5. 面積のオーバーヘッド抑制手法の評価

## 5.1 評価環境

提案する限定方法の評価環境を示す.評価対象回路には株式会社東芝社の Media Embeded Procsessor (MeP) コアと (株) ルネサステクノロジ社の M32R を用いた.ライブラリは表 1 に示す 65nm のスタンダードセルライブラリを用いている.論理合成は,表 1 の電源電圧 1.3V のスタンダードセルライブラリを用いて Synopsys 社の DesignCompiler で行っている.表 2 に対象回路の構成を示す.クロック周期は合成時のタイミングレポートを基に決定している.

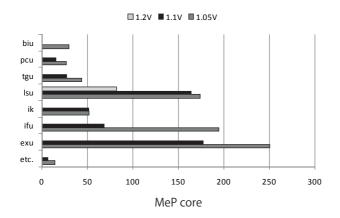

# 5.2 タイミングエラーに遭遇する FF の解析

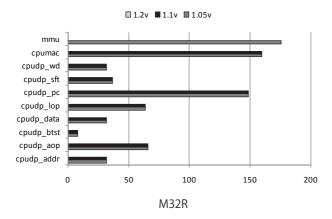

電源電圧を 1.05V-1.2V の間で変化させたときにタイミング 違反 FF 数をユニットごとに解析した結果を図 4 に示す.縦軸 のそれぞれは各評価回路内のユニットを示している.また,横軸 はユニット内のタイミング違反 FF の数を示している.MeP コアでは 1.2V のときロードストアユニット (lsu) 内でのみタイミング違反 FF が検出された.さらに,電源電圧を 1.1V,1.05V にすると実行ユニット (exu) とインストラクションフェッチュニット (ifu) 内でタイミング違反 FF が増加していることがわかる.

一方, M32R の場合, 1.2V ではタイミング違反 FF は検出

(注1): ここでは,素子特性に影響する要因を電源電圧に限定して説明している.

図 4 ユニットごとのタイミングエラーに遭遇する FF 数

されなかったが,1.1V,1.05V と電圧を下げるとタイミング違反 FF が検出された.特に積和演算ユニット(cpumac)とプログラムカウンタの制御ユニット( $cpudp\_pc$ )内で多くタイミングエラーが発生することがグラフからわかる.また,メモリマネージメントユニット(mmu)に注目すると 1.1V まではタイミング違反 FF が検出されていないが,1.05V に電圧を下げるとタイミング違反 FF が他のユニットよりも多く検出されていることがわかる.

図 4 に示したユニットはタイミング違反 FF が検出されたユ ニットのみであり、タイミング違反 FF が検出されなかったユ ニットは省略している.このようにタイミング違反 FF が特定 のユニットへ偏っていると、それらのユニットのタイミング制 約を満たすように電源電圧が決定される.これにより,その他 のユニットに十分なタイミングマージンが存在しても電源電圧 をそれ以上下げることはできない.この対策として考えられる のは, DVS の粒度をチップ全体からより細粒度なユニットごと の制御にすることである. ユニットごとに DVS を行えば,回 路遅延の短いタイミングに余裕のあるユニットはさらに電源電 圧を下げることが可能となる. ただし, ユニットごとに DVS を行うとそれら一つ一つに対してタイミング解析を行いカナリ アの挿入位置を限定する必要がある.これは,解析コストを増 加させる.また,それぞれのユニットに少なくとも一つ以上の カナリア FF を挿入する必要があるため挿入するカナリア FF 数も増加する.さらに, DVS のための付加回路もユニットの 数だけ必要となるため面積と消費電力に大きな影響を与え兼ね

図 5 カナリア FF の限定数と面積のオーバーヘッド

ない. したがって, DVS を細粒度にすることによる消費電力削減効果と付加回路による面積と消費電力のオーバーヘッドのトレードオフが重要となる.

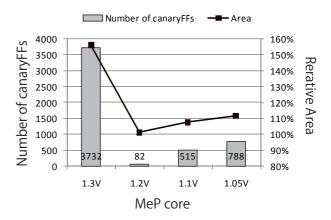

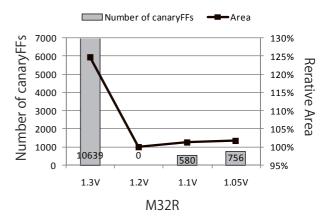

### 5.3 面積のオーバーヘッドの抑制効果

次に,タイミング違反 FF 数とそれらをカナリア FF で置き 換えた場合の面積のオーバーヘッドを図5に示す.棒グラフは カナリア FF へ置き換えた FF の総数を示している. また折れ 線グラフはカナリア FF に置換する前の面積を 100% として 通常の FF をカナリア FF へ置き換えた場合の面積のオーバー ヘッドを示している. ただし, 通常の FF をカナリア FF に置 き換えたときの面積のオーバーヘッドのみ考慮する.つまり, エラー予報収集回路と DVS のための付加回路のオーバーヘッ ドは考慮できていない.また,今回の面積にはキャッシュの面 積は含まれていない.カナリア FF 一つの面積は通常の FF の 3 倍と仮定する.レイアウトの評価では,通常の FF の面積の 約2.65 倍という結果が得られているが,この結果はカナリア FF を構成するゲートをライブラリの中から面積最小のものを 選択した場合の値である.したがって,遅延素子の遅延量やそ の他の回路の駆動力を考慮した場合,面積は増加すると考えら れる. そこで今回は通常の FF の面積の 3 倍と仮定している. グラフの 1.3V は全ての FF をカナリア FF に置き換えた場合 の値を示している . また 1.2V-1.05V はそれぞれのライブラリ を用いてタイミング解析を行い、タイミング違反 FF をカナリ ア FF で置換した場合の値を示している.

電源電圧が  $1.2\mathrm{V}$  のときに着目する . MeP コアの場合タイミング違反 FF は 82 個と少なく ,  $\mathrm{M32R}$  の場合では全くタイミング違反 FF は存在しなかった . これは , 評価の温度条件が 25 °C かつプロセス条件が Typical であったためであると考えられる . 最悪ケースの条件でタイミング解析を行えばさらにタイミング違反 FF は増加すると考えられる .

MeP コアの場合,1.05V のときにタイミング違反 FF は 778 個で,FF の総数の約 21% である.したがって,これらの FF をカナリア FF に置き換えたときの面積のオーバーヘッドはカナリア FF を適用していない場合と比べ約 12%の増加に抑えられることがわかる.また,M32R の場合,1.05V のときにタイミング違反 FF は 756 個で,FF の総数のわずか 7%程度である.したがって,カナリア FF に置き換えることによる面積のオーバーヘッドはカナリア FF を適用していない場合と比べ約 2%の増加に抑えられることがわかる.このことから,提案するカナリア FF の挿入位置限定手法は有効であると考えられる.また,本手法はカナリア FF だけでなく関連研究であるその他のタイミングエラー検出 FF の挿入位置の限定としても利用できる.

## 6. 今後の課題

本実験では,ライブラリの電源電圧のバリエーションに制限があるため,1.05V以下でどの程度タイミング違反 FF が存在するかは不明である.しかしながら,図 5 の傾向から予測すると,より低い電源電圧でタイミング違反 FF の数が増加することは容易に考えられる.置き換える FF の数が増加すれば面積だけでなく,カナリア FF の増加による消費エネルギーが増加する.したがって,DVSによる消費エネルギーの削減効果とカナリア FF の増加による消費エネルギーの増加を考慮した電源電圧の最適な点が存在する.今後はこの DVS による消費エネルギーの削減効果とカナリア FF の増加による消費エネルギーのトレードオフを評価する必要がある.

さらに,タイミングエラー予報収集のための回路および DVS を行うための回路による面積とそれらの消費エネルギーを考慮して評価を行う必要がある.PEDFF [7] では下限電源電圧を決定するために DVS による消費エネルギーの削減効果と付加回路による消費エネルギーのトレードオフを調査し,消費エネルギー削減効果の最もよい電源電圧を調査している.

また、提案するカナリア FF の挿入位置の限定方法は、論理合成後の回路のタイミング解析を基に挿入位置を決定している.このため、より正確に挿入位置を限定するためには、配置配線後の回路に対して解析を行う必要がある.さらには、カナリア FF を挿入することによってふたたび、配置配線を行う必要がある.配置配線が変われば回路のパス遅延は変化するので、カナリア FF を挿入することで新たにタイミングエラーを引き起こすパスが発生する可能性がある.したがって、配置配線を行い配線遅延を考慮した回路に対して、カナリア FF の挿入位置を限定するとともに、挿入後に変化する回路遅延に対する対策を検討する必要がある.

# 7. ま と め

カナリア FF を利用する DVS システムにおける面積のオーバーヘッドを抑制するために,カナリア FF の挿入位置を限定する方法の検討を行った.全ての FF をカナリア FF に置き換える場合,MeP コアで非 DVS の約 55%面積が増加する.そこで,下限電圧選択時のコーナー条件が最悪ケースの場合にタイミングエラーが発生する FF のみをカナリア FF に置き換えることで面積のオーバーヘッドを抑制することを検討した.その結果,MeP コアでは上限電圧を 1.3V とし下限電圧を 1.05V とする場合で面積の増加を約 11% に抑えることができることが明らかとなった.M32R では全ての FF をカナリア FF に置き換える場合非 DVS の 25%面積が増加するのに対してわずか 2% の面積増加に抑えることができる.

面積のオーバーヘッドの問題は,カナリア FF 同様にタイミングエラー検出 FF を利用する DVS システムにおいて共通の問題であるため,挿入位置の限定は同様に有効である.

#### 謝辞

本研究の一部は,科学研究費補助金・基盤 A(No.19200004), 基盤 B(No.20300019), および科学技術振興機構 CREST プロジェクトの支援によるものである.なお,実験に使用した回路の合成は株式会社東芝および東京大学大規模集積システム設計教育研究センターを通じ株式会社半導体理工学研究センター,(株)イー・シャトル,富士通株式会社,(株)ルネサステクノロジ,シノプシス(株)の協力で行われたものである.

## 文 献

- [1] D. Blaauw, S. Kalaiselvan, K. Lai, S. Wei-Hsiang, C. Tokunaga, S. Das, and D. Bull, "RazorII: In Situ Error Detectionand Correctionfor PVT and SER Tolerance", International Solid-State Circuits Conference, pp.400-622, 2008.

- [2] S. Borkar, T. Karnik, S. Narendra, J. Tschanz, A. Keshavarzi, and V. De, "Parameter Variations and Impacton Circuitsand Microarchitecture", Annual ACM IEEE Design Automation Conference, pp.338-342, 2003.

- [3] D. Ernst, N. S. Kim, S. Das, S. Pant, R. Rao, T. Pham, C. Ziesler, D. Blaauw, T. Austin, K. Flautner, and T. Mudge, "Razor: ALow-Power Pipeline Based on Circuit-Level Timing Speculation", 36th International Symposiumon Microarchitecture, pp.7-18, 2003.

- [4] K. Hirose, Y. Manzawa, M. Goshima, and S. Sakai, "Delay-Compensation Flip-Flops for Timing-Error Tolerant Circuit Design", International Conferenceon Solid State Devices and Materials, pp.480-481, 2007.

- [5] T. Sato, and Y. Kunitake, "Critical Issues Regarding A Variation Resilient Flip-Flop", 14th Workshopon Synthesis and System Integration of Mixed Information Technologies, pp. 280-286, 2007.

- [6] O. Unsal, J. Tschanz, K. Bowman, V. De, X. Vera, A. Gonzales, and O. Ergin, "Parameter Variations and Impact on Circuits and Microarchitecture," IEEE Micro, Vol.26, No.6, pp.30-39, 2006.

- [7] 栗本昌憲, 鈴木弘明, 秋山励, 山中唯生, 大熊晴之, 高田英裕, 篠原尋史, "エラー検出 FF を用いた DVS における Short Path Penalty と OR-Tree Latency の低減手法", 電子情報通信学会招待講演 VLD, Vol.2008, No47, 2008...